NOC Research Group

Welcome to the website of the NOC Research Group @ IMD as a platform to present our ongoing research in the challenging field of Networks-On-Chip (NOC).

NOCs have been proposed as a new design methodology to cope with the increasing number of problems in nanometer technology. NOCs consist of heterogeneous resources that are encapsulated from another which allows the use of different voltages, frequencies or even diverse technologies for each resource.

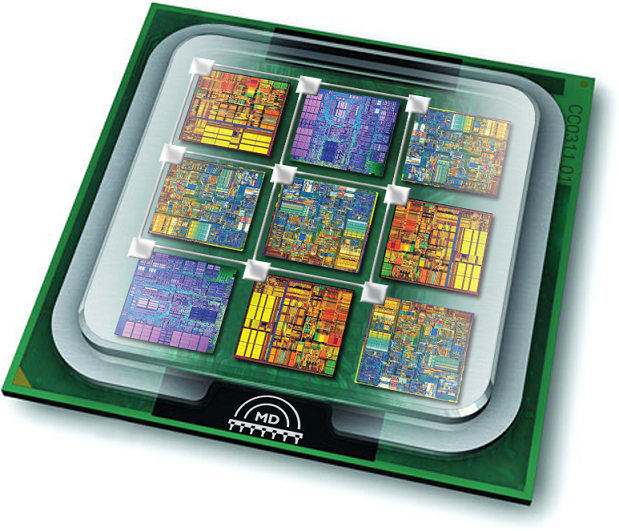

Furthermore, encapsulation eases the exchange and reuse of resources as well as the integration of intellectual property. The independent resources are connected (through a determined interface) to an on-chip network which affords the communication among the resources whereas the network consists of routers and physical links. An example of a simple topology with the mentioned components is shown in figure 1.

Current challenging projects

Please refer to the corresponding sections for detailed information on the current projects within the NOC Research Group @ IMD:

- Low Power

Multi-layered system approach to achieve an optimal overall power efficiency

- Reliability

Combination of low-level fault-avoidance/-detection and high-level reliability management

- Applications

Stream-based applications with high demands for throughput and concurrent execution

- Reconfiguration

Dynamically reconfigurable system design with an extended operating system - High level system design and simulation

Behavioral simulation of complex NoC-based systems for early and fast design space exploration - Modeling of operating parameters

Power estimation and simulation of thermal behavior - Thermal-aware System Management

Runtime system management to improve temperature profiles - Signal Integrity

Handling of phenomena impairing the signal integrity of highly integrated circuits