Thermal-aware System Management

The progress of deep submicron technology leads to rising power densities and switching activities per unit area. This abets thermal stress and various other temperature related issues, since a most of the consumed power is dissipated as heat. Additionally, due to device miniaturization nanoelectronic systems become increasingly prone to failures induced by high on-chip temperatures and temperature variations as well as temperature gradients across the chip.

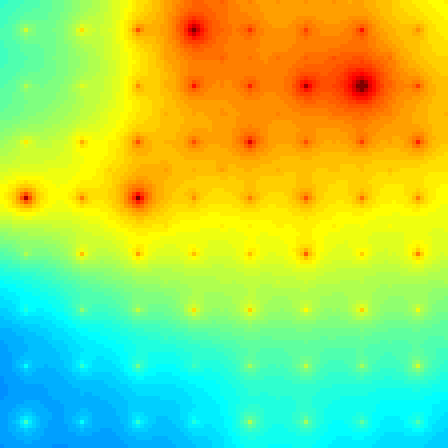

This development necessitates effective mechanisms for temperature aware system design and thermal management during system operation. Particularly, sophisticated approaches for quick and yet sufficiently accurate estimation and computation of on-chip temperature distribution and its development over time are in great demand. Design space exploration for reconfigurable systems like FPGA-based implementations significantly benefits from such approaches, since the thermal impact of different configurations can be analyzed in advance. This serves to avoid hot spots and thermal imbalances. Furthermore, such techniques may be employed for adaptive runtime thermal management of Systems-on-Chip and reconfigurable systems.

Suitable approaches for temperature estimation and computation have to fulfill various requirements such as adaptivity and flexibility to be applicable for reconfigurable systems. For FPGA-based systems the technique of applying ring oscillators consisting of inverter chains in order to estimate temperature in certain region of the FPGA may be used. This approach reverts to the dependency of the on-chip signal propagation delay on temperature. Another general approach suitable for both FPGA-based and ASIC systems is to estimate the temperature based the on-chip switching activity and the equivalence of thermal and electrical energy flows.